For Lithography, Placement Is Key

"A human hair is huge."

While EUV gets a lot of attention, today's chips depend upon 193-nm lithography. This is likely to continue to be the case for years to come for all but the most demanding layers. Thus, the 193-nm workhorse of semiconductor manufacturing will have to continue to up its game, and that means dealing with edge placement errors.

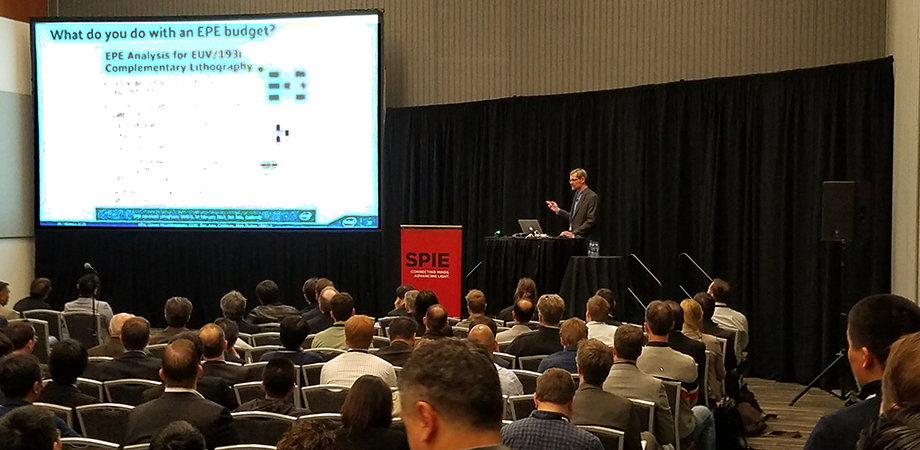

That was the message from Mark Phillips, Intel's director of lithography hardware and solutions, in a keynote address on Tuesday, 26 February at the SPIE Advanced Lithography symposium. In outlining the issues around running a process utilizing both extreme ultraviolet (EUV) and deep ultraviolet (193-nm) lithography, Phillips noted, "I viewed this edge placement error as the biggest thing we had to sort out."

A chip is built by laying down, patterning, and then etching a series of conducting and insulating layers. Therefore, the alignment of a layer to the one above and below is key to making everything work. So, keeping the edge placement error to an acceptable level is important. That value depends upon the process, but it must be less than the feature size. For an advanced process, say a 10-nm node, this means the edge placement error may only be at most a few nanometers for the most stringent layers.

The minimum pitch, or how closely things can be packed together, is found by multiplying the edge placement error by a constant, according to Phillips. But the constant is not a simple value. It depends on the layout geometry, the films, and the process. That's because the edge is a 3D affair. As a contact, for instance, etched down through a film, may be large at the top while tapering down at the bottom or vice versa. So, edge location depends on where it is measured along the length of the hole.

Failure to keep edges far enough apart will mean that some circuitry that shouldn't touch will, leading to a potentially chip-killing defect. Edges that are too far apart, on the other hand, may mean that items that should touch won't, again possibly rendering a chip inoperable.

There will be trillions of through-holes, transistors and the like on upcoming devices. So, the acceptable error rate of killer defects will have to be parts-per-trillion.

In the case of edge placement errors, these must be reduced, even if due to random events, Philips said. If that is not possible, then a work around needs to be implemented. The ability to measure edge placement all along a structure will also have to be developed, with the incentive to do so an economic one.

"When yield is limited by edge placement error (EPE), metrology has a compelling ROI," Phillips said.

In the second keynote, Yuri Granik, chief scientist at Mentor, discussed semiconductor manufacturing software and process modeling. That would be helpful in determining the impact of taller resist layers or other potential process changes on edge placement error. There are traditional ways to do such modeling, but they can be complex and take a long time to run. Neural networks could make the modeling more efficient, but they are probably not the best approach, according to Granik.

"The most beneficial would be to consider hybrid ANN (artificial neural networks) and traditional models," he said.

Modeling improvements are needed because the process is growing more complex at the same time the margin for error is shrinking as feature size does. Citing calculations done by others, Granik noted that the upcoming 5-nm technology node has features about equal to how much a human hair grows in a second. So, what is tiny in everyday experience is not in the world of semiconductor manufacturing.

"A human hair is huge," Granik said.

Hank Hogan is a science writer based in Reno, Nevada.

See more news and highlights from SPIE Advanced Lithography.

| Enjoy this article? Get similar news in your inbox |

|