Using directed self-assembly to manufacture field-effect transistor circuits

The adoption of restricted designs for semiconductors (e.g., grating-like patterns) has promoted the use of 193nm multiple patterning and complex computational techniques in scaling. As patterning now approaches the 7nm node (i.e., with minimum feature pitch of less than 30nm and feature size of less than 10nm), however, lithographers face new challenges in the use of quadruple patterning. For instance, it is difficult to simultaneously achieve tight process control over pattern uniformity in terms of critical dimension (CD), pitch, and overlay.

Extreme UV (EUV) lithography, which provides exceptional resolution, is seen as a strong contender to enable single-exposure processes and non-regular designs that would likely give the best process yields and circuit performances. EUV, however, faces challenges that have yet to be mitigated. These include low source power (which limits throughput), a lack of reliable pellicles (the thin membrane films that prevent particles coming into contact with the mask and introducing image defects), and non-zero phase defects buried in the mask.1 Directed self-assembly (DSA), based on material phase separation, offers an effective bottom-up approach. DSA is promising because it enables extremely low pitch (less than 20nm, or even down to 10nm with advanced DSA materials). Furthermore, it provides potentially unmatched CD uniformity. It also provides immunity to pitch walking (where the local line spacings within a grating are not constant), i.e., a problem that has plagued self-aligned double patterning (SADP) and—more severely—self-aligned quadruple patterning (SAQP).2

DSA is listed as an option for patterning line/space pitches at 20nm and below in the International Technology Roadmap (ITRS).3 To investigate if DSA can be used in manufacturing, however, it is necessary to closely examine the ‘knowns’ and ‘unknowns’ of the DSA approach. In our work, we are therefore investigating the following questions: Can the self-aligned DSA process be made4 to benefit the overlay process? Can DSA defects be brought down to the ITRS roadmap target (one defect/cm2)? Can we control line-edge roughness, or line-width roughness, to about 1nm (at the three-standard-deviation level)? Can DSA (which has inherent strength for regular patterns) support critical circuit design constructs for systems on chips (SoCs)? In particular, our work is focused on answering the last of these questions.4

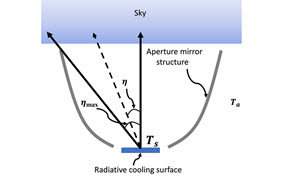

In resolution enhancement techniques, such as SADP, SAQP, and multiple litho-etch steps, a standardized approach is taken, whereas a variety of approaches are used in DSA methods. Each DSA version has its own set of design restrictions and process capabilities, and it is therefore not easy to provide a generic discussion of design technology co-optimization (DTCO). To further investigate DSA for SoC development, we first undertook qualitative DTCO by extracting critical constructs from circuit-relevant designs. We also screened various DSA processes to fulfill the most critical ground rules and process assumptions. We qualitatively illustrate in Figure 1 that several layers of fin field-effect transistors (FinFETs)—fins being the equivalent of the channel region in a planar metal–oxide–semiconductor field-effect transistor—from a standard cell library are DSA-friendly, while others are less so. This qualitative step is based on an experimental demonstration of basic structures.

When we had completed the qualitative DTCO phase, and down-selected the DSA candidate processes for particular design layers, we then undertook a quantitative DTCO flow. Our down-selected process candidates for this second phase are shown in Figure 2.5,6 We developed a suite of tools, including a fast DSA model to study the legality of certain constructs. For this, we used only a few of the most critical constructs selected from the extraction process for a realistic design.7A resultant quantitative DTCO flow for a layer of fins is depicted in Figure 3. In this process, we introduced several new features, including a DSA-compliance check, DSA guiding patterns, and fin-cut pattern generation. We also used a fast 3D DSA model to include lithographic pattern-guiding verification and a DSA verification step.8 We then classified the constructs as either DSA-compliant or non-compliant, and sent the latter for design tweaks.

A summary of our DTCO study on fins, based on the most critical constructs for a SoC design, is shown in Figure 4. We determined that a self-aligned DSA process is preferable to a conventional ‘sea-of-fins’ approach6 for overlay. We also found that this process has the capability of supporting various realistic design architectures of different track heights (see Figure 5).4 We conducted a simple test on unidirectional-routing metal wires, which indicates the feasibility of our method for standard cell architecture. We have also undertaken similar DTCO assessments for self-aligned via layers, in which we compare graphoepitaxy DSA, using conventional cylinder block co-polymers (BCPs), with lamella BCPs. From these investigations, we concluded that a lamella BCP process is preferable for self-alignment technology.4, 9

In summary, we have shown the feasibility of using DSA on several layers and different types of standard cell architectures for FinFET circuits. With our DTCO assessment, we move a step closer to manufacturing using DSA, and we can accelerate progress toward fully chip-worthy, circuit-relevant industrial demonstrations. We now need to make several improvements to our approach, including further reduction in DSA defects and tuning, to achieve the maximum DSA commensurability window for the desired morphologies. We are also working to produce novel and improved resolution enhancement techniques and fast DSA models, as well as the creation of DSA-compliant cell libraries and memory design for electronic design automation counterparts.

The authors acknowledge contributions from Jaime Morillo, Jed Pitera, Kristin Schmidt, Markus Brink, Daniel Sanders, Nelson Felix, and Sean Burns (all at IBM).

Kafai Lai is based at the T. J. Watson Research Center, where his focus is on lithography research and design technology co-optimization. He was chair of the 2012–2015 SPIE Optical Microlithography Conference, and has been a short-course instructor since 2005. He is a fellow of the Optical Society of America and SPIE, and is a senior member of IEEE.