# PHOTOMASK

BACUS-The international technical group of SPIE dedicated to the advancement of photomask technology.

Invited Paper 7985-4

# NGL Masks: Development Status and Issue

Naoya Hayashi, Electronic Device Operations, Dai Nippon Printing Co., Ltd., 2-2-1, Fukuoka, Fujimino-shi, Saitama, 356-8507, Japan; Tsukasa Abe, Yuichi Inazuki, Tadahiko Takikawa, and Hiroshi Mohri, Electronic Device Lab, Electronic Device Operations, Dai Nippon Printing Co., Ltd., 2-2-1, Fukuoka, Fujimino-shi, Saitama, 356-8507, Japan; Takeya Shimomura, Electronic Device Labs, DNP Corporation USA, 3235 Kifer Road, Suite 100, Santa Clara, CA 95051

#### **ABSTRACT**

Semiconductor lithography candidates toward 2xnm node and beyond include wide variety of options, such as extension of 193i, EUVL, NIL, and ML2. Most of those candidates, except ML2, need critical mask feature to realize effective high volume manufacturing. In this presentation, EUVL mask technology update and future issues will be presented.

#### 1. Introduction

There are several lithography candidates for 22/20 nm technology node, as Next Generation Lithography (NGL). Each candidate has some complexity and risk in mask fabrication and lithography process as shown in Table-1. Optical extension of current 193 immersion lithography needs multiple patterning with very complex mask pattern features. Extreme Ultra-violet Lithography (EUVL) is a candidate of NGL with very shorter wavelength of 13.5nm light source and single patterning step, with less complex pattern features. NIL templates have 1X patterns and are requiredmanufacturing process with higher resolution compared to that of the 4X photomasks for optical extension and EUVL. Mask Less Lithography (ML2) does not need ordinary masks, but has very slow throughput for manufacturing.

Continues on page 3.

8 materials

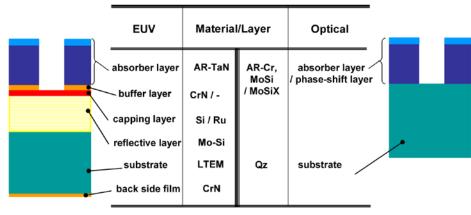

Figure 1. Comparison of mask substrate structures.

>85 layers

~3 layers 3 materials

#### TAKE A LOOK INSIDE:

INDUSTRY BRIEFS

-see page 9

CALENDAR

For a list of meetings

—see page 10

# EDITORIAL

## **Industry Veterans Weigh in** on EUV

Bryan Kasprowicz, Photronics, Inc.

Earlier this year, we held annual BACUS panel discussion at the SPIE Advanced Lithography Symposium. The theme for this discussion was "How to afford the infrastructure to support EUV and can masks be made at an affordable price?" We had several industry veterans share their thoughts.

Harry Levinson of GLOBALFOUNDRIES justified the EUV investment by comparing wafer cost to that for optical lithography, at throughputs of 125 and 200 WPH, respectively, highlighting the importance of mask cost amortized as wafer cost per chip, decreasing with higher wafer volume. Sean Doyle of Intel Capital and Andy Wall of Hoya discussed EUV investment strategy. Mr. Doyle focused on the mask market paradigms, how the key elements of productivity are related to the technology, customers and suppliers. He then offered a response, how to advance EUV through consortia and collaboration routes but also highlighted an opportunity for "mutualization" where there may be multi-party agreements or direct equity investments to foster market pull through demand alignment. Mr. Wall compared the current EUV blanks business environment to that of optical blanks and showed the significant investment (a 6:1 ratio over return) is required to support the current limited volume. He then suggested a simple outlay recovery model should the investments be made. Accordingly, the blanks company makes the investment required to deliver the blanks and recovers these investments through blank sales.

Brian Haas of KLA-Tencor presented their reticle inspection roadmap strategy down to the 11nm HP/8nm Logic nodes leveraging existing models and hinting at the development of an actinic platform. He went on to propose that broader EUV adoption will be based on the scanner throughput, assuming of course the mask manufacturing infrastructure is available. He suggested that an 80 WPH minimum is required to ensure affordability with double of that number necessary to allow full merchant mask manufacturer participation.

Naoya Hayashi of Dai Nippon Printing and Chris Progler of Photronics were of like mind that the EUV Mask Infrastructure will be expensive with limited opportunity to realize any returns within a reasonable period of time without commitments from the captive mask facilities. Hayashi-san suggested that joint ventures between the captives and the merchants as well as between the merchants may be necessary to aggregate enough mask volume to ease the burden of the capital investment. While Mr. Progler noted that due to the high costs and redundancy for business continuity, a merchant solution would benefit the industry in terms of competition, cost sharing and development. However, they concluded that the end user must realize these benefits and be willing to accept the costs of the technology, perhaps a new paradigm for the mask industry.

Lastly, John Warlaumont of Sematech highlighted some of the commercialization aspects of the EUV mask infrastructure (EMI). Given that there are a few IDM's that currently have EUV on their roadmap, the amount of investment required by them is significantly higher. This poses an infrastructure funding problem, especially for masks. In order to find a solution, Sematech launched the EMI and proposed funding models that are being well received. Mr. Warlaumont concluded that still, not everyone will be amenable to these models due to the technology innovation and cost.

Since this Advanced Lithography panel discussion, several more EUV systems have been installed, with more coming, and advanced learning is in the early stages. This demonstrates the seriousness of the interest in implementing this technology across all areas - memory and logic, foundry and IDM. Now the questions are, would there be enough IC demand for these advanced nodes requiring EUV, and when?

BACUS News is published monthly by SPIE for BACUS, the international technical group of SPIE dedicated to the advancement of photomask technology.

Managing Editor/Graphics Linda DeLano Advertising Teresa Roles-Meier BACUS Technical Group Manager Pat Wig

#### ■ 2011 BACUS Steering Committee ■

**President**Wolfgang Staud, *Applied Materia*

#### Vice-President

Larry S. Zurbrick, Agilent Techr

**Secretary** Artur Balasinski, *Cypress Semiconductor Corp.*

#### **Newsletter Editor**

Artur Balasinski, Cypress Semiconductor Corp.

**2011 Annual Photomask Conference Chairs** Wilhelm Maurer, *Infineon Technologies AG (Germany* Frank E. Abboud, *Intel Corp*.

#### **International Chair**

Naoya Hayashi, Dai Nippon Printing Co., Ltd. (Japan

#### **Education Chair**

Artur Balasinski, Cypress Semiconductor Corp.

Members at Large

Paul W. Ackmann, GLOBALFOUNDRIES Inc. Michael D. Archuletta, RAVE LLC

Uwe Behringer, UBC Microelectronics (Germany Peter D. Buck, Toppan Photomasks, In Brian Cha, Samsung Kevin Cummings, ASML US, Inc. Glenn R. Dickey, Shin-Etsu MicroSi, Ir Thomas B. Faure, IBM Corp. Brian J. Grenon, Grenon Consulting Jon Haines, Micron Technology Inc Mark T. Jee, HOYA Corp, USA Bryan S. Kasprowicz, *Photronics, Inc.* Oliver Kienzle, Carl Zeiss SMS GmbH (Germa M. Warren Montgomery, The College of Nanos Science and Engineering (CNSE) Emmanuel Rausa, Plasma-Therm LLC. Douglas J. Resnick, Molecular Imprints, Inc Steffen F. Schulze, Mentor Graphics Corp Jacek Tyminski, Nikon Precision Inc. John Whittey, KLA-Tencor MIE Div.

P.O. Box 10, Bellingham, WA 98227-0010 U Tel: +1 360 676 3290 or +1 888 504 8171 Fax: +1 360 647 1445 SPIE.org customerservice@spie.org

$N \bullet E \bullet W \bullet S$

Table 1. Complexity and risk of NGLs.

|                              |                           | Optical<br>Extension                  | EUV                                          | Nanoimprint                | Maskless<br>Lithography             |

|------------------------------|---------------------------|---------------------------------------|----------------------------------------------|----------------------------|-------------------------------------|

| Patterning & Mask Production | Mask materials            | Optimization and Standardization      | Very complex substrate stacks                | Standard Qz<br>substrate   | No mask used                        |

|                              | Data Prep                 | Very complex data<br>with SMO/ILT/DPL | Minimum data<br>prep for flare<br>correction | No OPC needed              | Compatibility with<br>Optical litho |

|                              | Pattern<br>Generation     | Massive shot counts/writing time      | Flat data exposure needed                    | 1x resolution              | 1x resolution and<br>Throughput     |

|                              | Processes                 | CD and defect control                 | Damage free process/Cleaning                 | Defect control             | Compatibility with Optical litho    |

|                              | Inspection &<br>Metrology | Very complex feature and spec.        | Actinic inspection & metrology               | Inspection and repair      | Resolution & Data base inspection   |

| Lithography                  | Throughput                | Multiple exposure                     | Source, resist,<br>mask life                 | Step & repeat time         | Massive parallel<br>beams needed    |

|                              | Mask cost                 | Multiple complex<br>masks needed      | High substrate and QA cost                   | Replication usable         | No mask used                        |

|                              | Readiness                 | Ready now                             | Pilot in 2011?                               | Tool/Feasibility<br>needed | Tool availability                   |

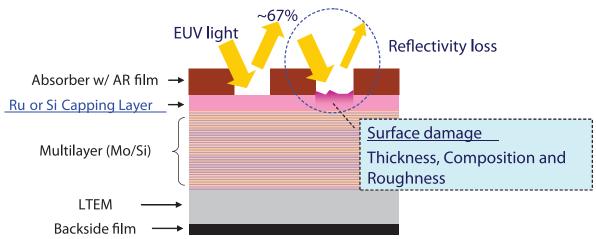

EUVL has been recognized as a preferred candidate for NGL with single exposure, relatively simple mask pattern feature, and 4X mask magnification as current optical lithography. On the other hands, EUV mask substrate has quite complex multi layer stacked feature as shown in Figure-1, and will be required very critical defect and flatness control. We have been evaluating both optical and electron beam (EB) inspection systems for EUVL mask[1,2]. In this paper, mask development status for EUVL are updated in mask qualities compared with ITRS requirements[3], and also in mask cleaning and defect inspection technologies.

#### 2. Experiment

Blank substrates of EUVL mask for evaluation are provided by HOYA with Si- and Ru-Capping structures on the mirror layers with TaN based absorber layer on the top. Mask fabrication was done with 50KeV VSB mask writer, JBX-3040 and EBM-7000 using CAR and Non-CAR processes. For measurement tools, we used "LWM9000" (Advantest) CD-SEM, "LMS IPRO" (KLA-Tencor) image placement measurement tool.

DUV optical mask inspection system "NPI-6000EUValpha" (Nu-Flare), and Mask EBI system "eXploreTM 5200" of Hermes Microvision, Inc., were used as EUV mask pattern defect inspection tool.

#### 3. Results and Discussion

#### 3-1. Mask pattern qualities

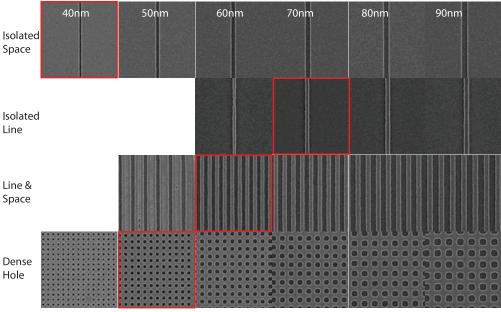

Figure-2 shows the absorber pattern resolution of EUV mask written by EBM-7000. We confirmed the resolution of 40nm, 70nm, 60nm, and 50nm on isolated space, isolated line, lines & spaces, and dense hole array, respectively. Those results satisfied ITRS requirement of 78nm at 2013 [3].

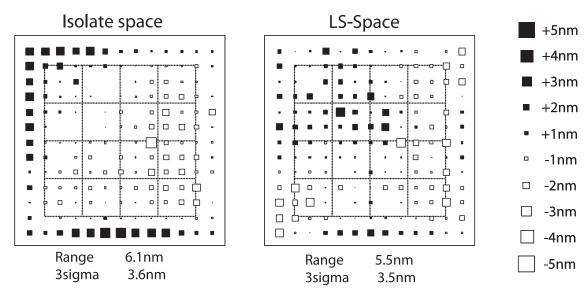

The results of absorber pattern CD (Critical Dimension) uniformity across the EUV mask is shown in Figure-3. It shows 3.6nm and 3.5nm in 3-sigma on isolated space and space of lines & space patterns respectively. Those results were close to ITRS require-

ment of 3.0nm at 2013.

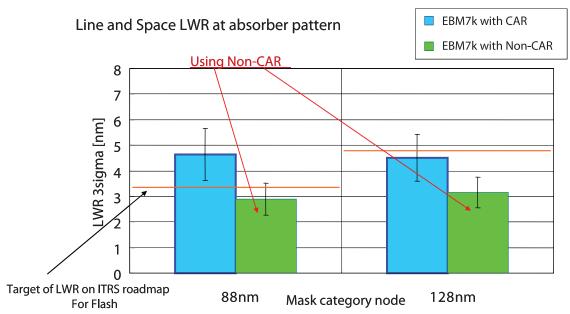

The line width roughness of EUV mask using chemical amplitude resist (CAR) and non-CAR on 128nm line and space design feature and 88nm one written by EBM-7000 system is shown in Figure-4. With non-CAR, line width roughness of both 128nm and 88nm were about 3nm and satisfied the ITRS requirements. On the other hand, general CAR needs further improvement for 88nm, which equivalent to 22nm HP node.

#### 3-2. EUV mask cleaning

Figure-5 shows EUV specific mask cleaning issues. There will be some damage in the capping layer, which consists of Ru or Si, during mask cleaning cycle in the FAB to remove the particle and contamination. Due to no-pellicle applied on EUV mask, more frequently cleaning will be needed.

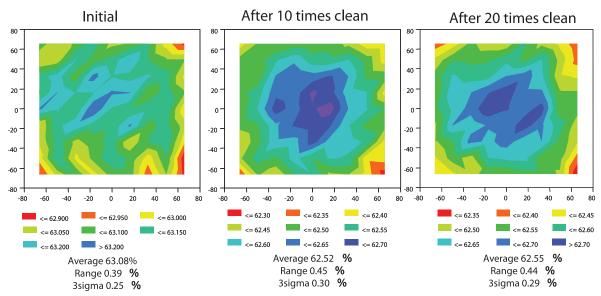

The results of reflectivity change after mask cleaning by general SPM and SC1 cleaning method on Ru capping structure is shown in Figure-6. Initial several cleaning cycle may remove Ru-oxide on the surface and change the reflectivity uniformity signature. Additional cleaning will not affect on further reflectivity change because of sufficient durability of Ru capping layer.

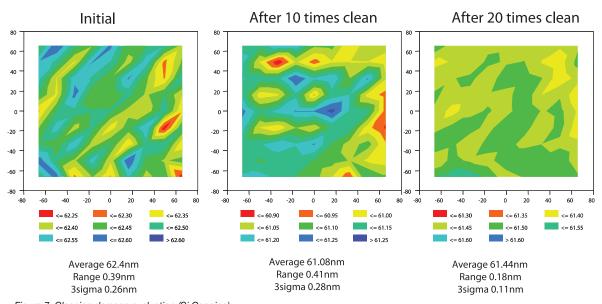

On the other hand, Figure-7 shows the results of same on Si capping structure. General cleaning method may cause continuous damage, which thinning the Si capping layer, along with the cleaning.

We need appropriate cleaning method which may not cause damage on any capping layer and also absorber layer.

#### 3-2. Defect inspection methods and evaluation results

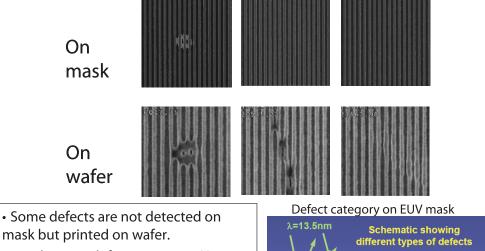

Figure-8 shows the printability evaluation results and defect type on EUVL mask. We found that some defect on EUVL mask could not be seen with current mask inspection tool, but be printed on wafer. So called "Phase defect" will exist in multi layer, and will be printed on wafer with even very small height, less than 2nm, on the surface. Inspection tool vendors have been trying to capture the defect with optical source tool and EB tool[2,4,5,6]. However,

Figure 2. Patterning performance of EUVL mask.

#### Target pattern size 180nm: pattern area size 132x132mm

Figure 3. CD uniformity of absorber pattern.

we think that we need actinic, with EUV light source, blank defect inspection tool to capture the "Phase defect" at the stage of EUV mask blank manufacturing.

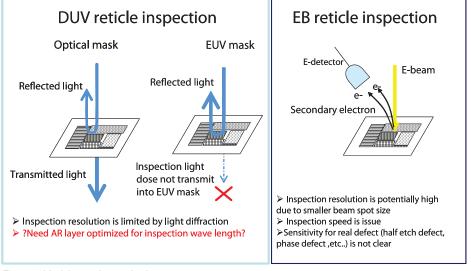

The general inspection methods for optical mask and EUV mask are shown in Figure-9. Current existent mask inspection system with DUV light source was designed using both transmitted light and reflected light to capture various types of defects on the optical mask. On the other hand, EUV mask substrate does not have the capability to transmit the DUV light, which limited the capability

and sensitivity of inspection system for EUV mask. The inspection system with electron beam (EB) source has been considering to be applied for EUV mask by using reflected secondary electron to capture the defect with better resolution. However, the throughput of EB inspection system is very slow due to very small pixel size for inspection.

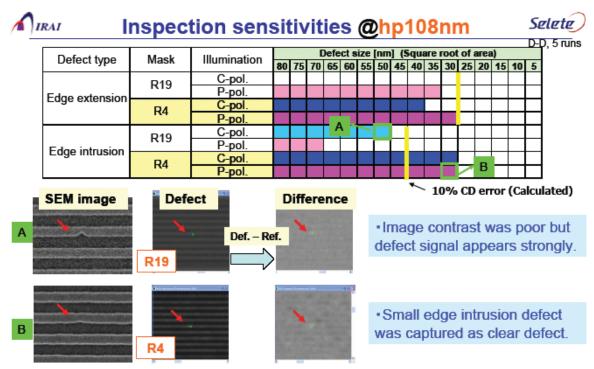

Figure-10 shows the inspection results of designed defect EUV mask by DUV optical source inspection tool, NPI-6000EUValpha with 199nm wavelength light source and polarized illumination. We

Figure 4. LWR evaluation results on EUVL mask.

Figure 5. EUV mask cleaning damage.

found that low reflective absorber layer and polarized illumination will enhance the contrast of the image, and improve the defect inspection sensitivity. The results showed that the sensitivity satisfied the requirement for 27nm HP features [7].

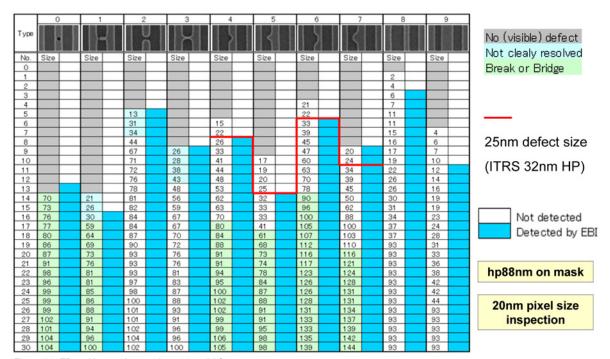

The evaluation result of EB inspection tool, eXplore 5200, on the designed defect EUV mask with 22nm lines and spaces is shown in Figure 11. The result showed the capability of capturing 25nm defect size, which reaches ITRS 32nm HP requirement.

Both inspection methods still need further improvement to reach to the 22nm HP requirement with enough stability and reasonable inspection cycle time.

#### 4. Summary

We have been developing EUVL mask using and modifying current photomask manufacturing technology. The qualities of EUVL mask have been achieving the requirement of 32nm HP generation at 2013.

We still need further study and development for EUVL mask cleaning, and defect inspection method to guaranty the printability and yield on wafer.

#### 5. Acknowledgment

The authors would like to thank Selete for optical defect inspection tool evaluation and Hermes Microvision, Inc. for EB tool evaluation.

We also express our thanks to DNP members involved in this work

#### 6. REFFERENCE

- Tsukasa Abe, Fujii Akiko, Sasaki Shiho, Mohri Hiroshi, Imai Hidemichi, Hironobu Takaya, Yasushi Sato, Naoya Hayashi and Yumiko Maenaka, "EUV mask pattern inspection using current DUV reticle inspection tool", Proc. SPIE, 6607, 66070L (2007)

- Takeya Shimomura, Yuichi Inazuki, Tukasa Abe, Tadahiko Takikawa, Yasutaka Morikawa, Hiroshi Mohri, Naoya Hayashi, Fei Wang, Long (Eric) Ma, Yan Zhao, Chiyan Kuan, Hong Xiao, and Jack Jau "EUV mask pattern inspection with an advanced electron beam inspection system", Proc. SPIE, 7520, 75201D (2009)

#### Ru cap EUV reflectivity damage

Figure 6. Cleaning damage evaluation (Ru Capping).

#### Si cap EUV reflectivity damage

Figure 7. Cleaning damage evaluation (Si Capping).

- 3. 2009 ITRS Lithography roadmap, Table LITH5C, http://www.itrs.net

- Ryoichi Hirano, Nobutaka Kikuiri, Masatoshi Hirono, Riki Ogawa, Hiroyuki Sigemura, Kenichi Takahara and Hideki Hashimoto "A novel defect detection optical system using 199-nm light source for EUVL mask", Proc. SPIE, 7638, 76382Z (2010)

- Shmoolik Mangan, Aya Kantor, Nir Shoshani, Asaf Jaffe, and Dror kasimov "Results from a novel mask inspection by 193nm DUV system", Proc. SPIE, 7638, 76383S (2010)

- Daniel Wack, Qiang Q, Zhang, Gregg Inderhees, and Dan Lopez "EUV mask inspection with 193 nm inspector for 32 and 22 nm HP", Proc. SPIE 7748, 77481Y (2010)

- Tsuyoshi Amano, Hiroyuki Shigemura, Noriaki Takagi, Tsuneo Terasawa, Osamu Suga, Hideaki Hashimoto, Masanori Saito, Ryoichi Hirano, and Nobutaka Kikuiri "EUV mask pattern defect inspection using 199-nm inspection optics", 2009 International Symposium on EUVL

mask but printed on wafer.

Need actinic defect inspection??

Size definition of Phase defect

<2nm height phase defect may print on hp22nm pattern

Absorber Capping layer Mo/Si ML Substrate Conductive film Cross-sectional view

Figure 8. Defect printability.

Figure 9. Mask inspection methods.

Figure 10. Optical tool inspection result on 27nm L&S.

Figure 11. EB tool inspection result on 22nm L&S.

# N • E • W • S

#### **Sponsorship Opportunities**

Sign up now for the best sponsorship opportunities for Photomask 2011 and Advanced Lithography 2011. Contact:

Teresa Roles-Meier Tel: +1 360 676 3290 teresar@spie.org

## Advertise in the BACUS News!

The BACUS Newsletter is the premier publication serving the photomask industry. For information on how to advertise, contact:

Teresa Roles-Meier Tel: +1 360 676 3290 teresar@spie.org

#### BACUS Corporate Members

Aprio Technologies, Inc.

ASML US, Inc.

Brion Technologies, Inc.

Coherent, Inc.

Corning Inc.

Gudeng Precision Industrial Co., Ltd.

Hamatech USA Inc.

Inko Industrial Corp.

JEOL USA Inc.

KLA-Tencor Corp.

Lasertec USA Inc.

Micronic Laser Systems AB

RSoft Design Group, Inc.

Synopsys, Inc.

Toppan Photomasks, Inc.

#### N • E • W • S

# **Industry Briefs**

## ■ CEA-Leti Annual Review: Update on maskless litho work

By Hughes Metras, U.S. Development, Leti June 28, 2011

Multi e-beam lithography, a maskless technology, is a recognized alternative to EUV on the International Technology Roadmap for Semiconductors for the 22nm node and below. But the technology must first overcome throughput, data handling and other challenges, Leti lithography program manager Serge Tedesco told Leti's 13th Annual Review in Grenoble, France. Leti, MAPPER Technology, and others partners launched the Imagine program in 2009 to assess the capabilities of multi e-beam technology against the needs of end users on a 300mm pilot line. The Imagine program's members include software, tool, materials suppliers, and chipmakers: Mentor Graphics, Aselta, Synopsis, SOKUDO, Nissan Chemical, Tokyo Electron, JSR, Dow EM, and MAPPER.

Tedesco said MAPPER will have a system with 13,000 parallel e-beams capable of producing 10 wafers/hour in 2013-14, to establish multi-beam technology infrastructure and demonstrate tool capability in terms of resolution, throughput, overlay, and stitching. By eliminating the need for photomasks, multi e-beam lithography would cut millions of dollars from the cost of manufacturing chips, and would open the doors for more designs and innovation.

#### ■ Lithography cost-of-ownership considerations

## By David K. Lam, Multibeam Corporation June 27, 2011

The semiconductor industry is facing major cost challenges in patterning advanced ICs in high volumes. A cost analysis by Burn Lin of TSMC, in 2009, projected the cost of lithography at the 22nm node, for optical, extreme ultraviolet (EUV) and multiple electron beams (MEB), at a throughput of 100 wafers/hour and excluding costs of EUV masks, infrastructure and power usage, etc., to be comparable.

Reality check #1. The EUV throughput of ASML's most recent EUV system, being installed at imec in May 2011, is 5-6wph, still considered a substantial improvement from previous versions, thanks to higher EUV source power, but almost 20X slower than the 100wph used in Lin's calculation. Lin also assumed that an EUV tool would cost 25% more than an 193i tool. Given 193i's current price tag of \$50 million, this formula puts EUV tool price at \$62.5 million. However, G. Dan Hutcheson of VLSI Research projected in November 2010 EUV tool cost to be \$125 million. This is 2X Lin's 2009 projection and 2.5X today's cost of a 193i tool. Nevertheless, EUV is making progress. A 5X boost in EUV source power, for example, could potentially increase throughput to 25-30wph for the \$125 million tool price.

Reality check #2. Mask infrastructure for EUV is still in development. SEMATECH in 2007 estimated that the average critical layer mask for EUV would cost \$300,000 and pattern 5000 wafers. This adds \$60 per layer. There remain unresolved issues in EUV infrastructure including mask blanks, mask making, defect inspection, and defect compensation — a requirement unique to EUV. On the other hand, complementary lithography, uses two lithography technologies to complement each other for better patterning at lower cost. Multibeam Corporation is developing CEBL for patterning critical layers for advanced logic and system-on-a-chip (SoC). CEBL focuses on cutting poly and metal lines as well as contact and via holes, while optically patterning all other layers. One version of CEBL is optimized for cutting applications and requires no masks.

Electron-beam lithography (EBL) tool price is tied to throughput. The desired 100wph for about €50 million (roughly \$71.4 million) puts pressure on EBL developers to increase throughput and reduce tool cost. EBL is too slow for high-volume manufacturing if used to pattern all layers. CEBL may play a limited yet crucial role: patterning only critical layers, with low feature density of ~5%. The scalable architecture delivers high throughout to complement and extend optical lithography. In addition, support infrastructure for CEBL is available today, thus eliminating major investments in new infrastructure.

# Join the premier professional organization for mask makers and mask users!

#### About the BACUS Group

Founded in 1980 by a group of chrome blank users wanting a single voice to interact with suppliers, BACUS has grown to become the largest and most widely known forum for the exchange of technical information of interest to photomask and reticle makers. BACUS joined SPIE in January of 1991 to expand the exchange of information with mask makers around the world.

The group sponsors an informative monthly meeting and newsletter, BACUS News. The BACUS annual Photomask Technology Symposium covers photomask technology, photomask processes, lithography, materials and resists, phase shift masks, inspection and repair, metrology, and quality and manufacturing management.

#### **Individual Membership Benefits include:**

- Subscription to BACUS News (monthly)

- Complimentary Subscription Semiconductor International magazine

- Eligibility to hold office on BACUS Steering Committee

spie.org/bacushome

#### **Corporate Membership Benefits include:**

- Three Voting Members in the SPIE General Membership

- Subscription to BACUS News (monthly)

- One online SPIE Journal Subscription

- Listed as a Corporate Member in the BACUS Monthly Newsletter

spie.org/bacushome

#### 2011

#### SPIE Photomask Technology

19-22 September 2011 Monterey Marriott and Monterey Conference Center Monterey, California, USA spie.org/pm

#### 2012

#### Advanced Lithography

12-16 February 2012 San Jose Convention Center and San Jose Marriott San Jose, California, USA spie.org/alcall

Submit your Abstracts Now!

You are invited to submit events of interest for this calendar. Please send to lindad@spie.org; alternatively, email or fax to SPIE.

SPIE is an international society advancing light-based technologies.

International Headquarters P.O. Box 10, Bellingham, WA 98227-0010 USA Tel: +1 888 504 8171 or +1 360 676 3290 Fax: +1 360 647 1445 customerservice@spie.org • SPIE.org

Shipping Address 1000 20th St., Bellingham, WA 98225-6705 USA

#### **SPIE** Europe

2 Alexandra Gate, Ffordd Pengam, Cardiff, CF24 2SA, UK

Tel: +44 29 2089 4747 Fax: +44 29 2089 4750

spieeurope@spieeurope.org • www.spieeurope.org